# Original Article

# Cube Stripping Function and Logic Restoration Based Hardware Security

Suresh Kannan P<sup>1</sup>, Rangarajan.J<sup>2</sup>, Selvi C<sup>3</sup>

<sup>1,2,3</sup>Department of Electronics and Communication Engineering, Muthayammal Engineering College, Nammakal, Tamil Nadu, India

Abstract: Guaranteeing security without compromising the exhibition and adaptability of a gadget is basically an exceptionally difficult endeavor for Researchers and Practitioners Approximate circuits (AxCs) tradeoff computational exactness against upgrades in equipment place, put off, or power consumption. IP center transporters who need to make such circuits need to persuade clients regarding the subsequent guess superior grade. As an answer, underwrite PUF based absolutely confirmation conveying AxCs. the vender makes a surmised IP center by and large with an authentication that demonstrates the estimation fine. The proof endorsement is packaged with the surmised IP center and shipped off to the client. We utilize the PUF reaction to free the element of the chip. The benefactor can authoritatively confirm the guess good of the IP center at a section of the standard computational expense for formal confirmation.

Keywords: Power Consumption, Hardware, Cube Stripping.

#### INTRODUCTION

Wellbeing has come to be a top-notch circumstance for integrated circuits (ICs) because of globalization and rethought seaward creation. for the term of the lifecycle of the IC, the chip may be underneath assault from overproduction throughout the assembling stage to unapproved reusing after benefactor attitude [1]. besides, a maker could make more chips through cloning over the assembling stage subsequent to gaining the plan via picking apart [2,3]. nation of the workmanship IC figuring out is better than the point that the chips might be picked apart inside certain weeks. There are committed enterprises that do inverse designing of new plug chips. accordingly, a plan is expected to forestall the assembling of unlawful cloned chips by means of figuring out.

equipment muddling is a technique to forestall IC theft and figuring out. equipment jumbling can be arranged into types: sound judgment or intentional locking and disguise, the primary thought toward the rear of coherent locking confusion is that piece of the design is changed with a configurable module on the format degree. In the event that the module isn't initiated via the dressmaker, the chip will now not work as expected [4-7]. for the term of the set upmanufacture enactment way in a depended-on plan house, the chips might be initiated by means of opening the muddled trademark with a secret key that might be scorched into on-chip wires. the ones opened chips can then be proposed to the open commercial center. The saved key can't be recuperated without direct admittance to the on-chip wires alongside with testing assaults. hence, an aggressor can't figure out the design on account of the confusion, and the chip can't be overproduced with out ability of the key. moreover, design degree strategies comprehensive of cell disguise [8] will be utilized as equipment muddling and faker contacts are utilized to protect contrary to aggressors. The organization of in vogue cells with various functionalities is made to seem indistinguishable in the cover approach. Covering could make it more hard to distinguish disguised entryways with robotized picture devices. in this paper, we have zeroed in on rationale locking-based equipment jumbling. various theoretically new and exciting techniques have been proposed to present sorts of confusion or presence of mind locking

to save you inverse designing and theft. as a case, additional unique OR (XOR) entryways might be embedded in combinational plans with configurable pieces that need to set productively to set off the chips [6]. Sham states might be embedded into limited country machines in consecutive plans, requiring positive arrangements of contributions to be executed for the circuits to trademark effectively [9]. Scrambling the interconnection network in a change based approach will reason the circuit to best works of art with a precise key to design the interconnection network [10]. other work has stowed away pieces of the circuit in a configurable exploration work area (LUT) [11]. With those obscurity strategies, the work for an aggressor to find the fitting key will turn out to be computationally infeasible [12]. the supposition made with these methodologies is that there is no immediate admittance to the significant thing content.

A problem with a large number of these techniques is that the key isn't specific across all cases of the chip. consequently, assuming that an aggressor is fit for recover the key by some methodology, it could free all chips and effectively overproduce the chips. recently, genuinely unclonable capacities (PUFs) had been utilized as a method for offering specific keys for muddling [14-16]. PUFs are intrinsic circuit natives that separate arbitrariness from the actual qualities of a gadget at the assembling stage [17,18] by utilizing applying input difficulties and gazing indiscriminately yield reactions. PUFs are smooth and easy to place into impact anyway their arbitrary nature ideally makes its conduct hard to foresee and form for an assailant.

some of those PUF-based absolutely muddling strategies require a total portrayal of the PUF input-yield response, along these lines requiring a minuscule result space for the PUF. Such PUFs are alluded to as weak PUFs. An untrusted foundry ought to do the equivalent portrayal and will keep the test response matches (CRP) for all chips sooner than sending them to the plan home. In the event that a key spilled from an initiated chip, the untrusted foundry should recuperate the whole format with the released key and, utilizing its PUF portrayals, have the option to let loose all chips whether approved or no more.

solid PUFs, then again, have an absolutely enormous information/yield space, making portrayal unrealistic and hence a decent arrangement extra loose. however, at the equivalent time, it makes some PUF-basically based confusions strategies infeasible. ideally, let's have an obscurity plot that might take gain of areas of strength for those to improve the security of the strategy. on this paper, PUF based absolutely proof wearing AxCs is proposed. the seller makes an estimated IP center all in all with an endorsements that demonstrates the guess quality. The evidence endorsement is packaged with the inexact IP center and despatched off to the client. The PUF reaction is utilized to open the trait of the chip.

The unwinding of the paper is ready as agree with: the portion 2 characterized the connected works of art of the articles and the part 3 is examined around the proposed technique for the compositions. The final product and discourse are characterized in component with the screen captures inside the portion four. in the end the paper is closed in fragment five individually. RELATED WORKS

Becker et al (2015) broke down the security super current IBS in total with an alright aggregate PUF as proposed at CHES 2011. considering the way that for an alright total PUF the conviction shiny new indistinguishable and autonomously disseminated reactions does now not hold, the discernment most recent spilled bits changed into brought at CHES 2011 to catch the security present day such developments. dependent absolutely upon an exquisite assessment the utilization of hamming distance portrayal and framework dominating procedures, we show that the entropy contemporary the significant thing acquired is essentially lower than expected.

Jiang et al (2017) proposed a green equipment design for cerebellar models utilizing inexact circuits with a little area and a low power. Utilizing the inborn bumbles resistance inside the cerebellum, surmised adders and multipliers are painstakingly assessed for executions in a versatile channel out basically based cerebellar model to accomplish an extraordinary tradeultra-modernf in exactness and equipment utilization.

## PROPOSED METHODOLOGY

In this paper, IC robbery is a tremendous security peril, where malevolent makers can deliver unapproved more prominent chips and additionally steal the records of a design through picking apart endeavors. As a countermeasure, equipment muddling plans by and large keep part of the format (which from that point is the "key") by utilizing transforming it with configurable modules. authorizing the configurable module to be full in with the kept key measurements empowers a post-fabricating enactment of each verify chip, yet with a need to country the danger of a released normal key. To verify that each chip has a remarkable key, substantial Unclonable capacities (PUFs) had been proposed to be consolidated with equipment obscurity and furthermore utilized for delivering a permit key, this sort of worldview is bound to utilize weak PUFs, in light of the fact that, to exceptionally set the significant thing (the substance of the configurable module) for each chip, the creator needs to describe the PUFs for every one of the chips completely. on this paper, we contend that a powerful aggressor inside the job of a producer can totally address all the feeble PUFs, and utilize any released key to interfere with the muddling structure. This work proposes major areas of strength for a fundamentally based equipment confusion plot by delivering a

permit key to effectively save you IC robbery even on account of a released key from a couple of actuated chip.

inside the proposed plot, the specific key with regards to chip comprises of two components: Key1, the substance material of the determination bits, and Key2, the substance material of the LUT. remember the most pessimistic scenario that the aggressor has achieved a duplicate of the total key, Key1, Key2, for a specific chip. clearly, this key can't be utilized straightforwardly to incite various chips. while heading to recuperate the grip key, the assailant must have a glance at the CRP space of the subset of the PUF that is utilized by the dressmaker for the spilled chip. resulting, we will talk about assorted potential assaults underneath any such circumstance:

- 1) PUF portrayal of chips in open commercial center: After getting a released key Key1 , Key2 from some chip, the assailant would be fit for recognize the subset of the PUF that is used by the clothier for that chip (from examining Key1). in any case, as all the portrayal channels of the PUFs have been taken out on the quit of the enactment procedure, describing the PUF is no longer to be had.

- 2) PUF portrayal of chips at assembling stage: At the creating degree, the portrayal channels are accessible to the assailant. notwithstanding, for the explanation that chips are not enacted at this point, the assailant can't have the "released key" to help propose which subset of the PUF may be utilized. The enormous CRP region of the hearty PUFs ensures that it's miles restrictively rich to comprehensively see every one of the CRPs in any event, for an unmarried PUF. as it was examined in area II-B, it is additionally restrictively extravagant for a maker to perform gadget concentrating on assaults on every one of the manufactured chips, wherein a comfortable solid PUF is utilized.

- 3) SAT-based absolutely attacks: without a prompt method for getting the CRP region of the PUFs, the assailant could form the total security at any point block (Obfuscator, PUF and the LUT) with an advanced LUT, after which attempt and find the substance material of such LUT through applying painstakingly planned essential contributions to a working chip and concentrating on the upsides of the main results. the critical idea to defeat such SATessentially based attacks is to painstakingly choose the kept element at the plan level, with the goal that the results of the LUTs become unequivocally corresponded. The proposed conspire in this artistic creations can works of art with many SAT-based absolutely counteraction plans to get a more powerful structure. additionally, the clothier can blast the assortment of q sham fan-outs took care of to the Obfuscator (as it became made sense of in area IV), for you to expand the worth of SAT-fundamentally based attacks through growing the size of the virtual LUT dramatically at a straight cost.

We utilize the setup of OCs of muddled plan to draw in with the PUF response with an end goal to create a chip-laid out permit to save you theft and overbuilding attacks and furnish the compensation in accordance with-gadget authorizing supplier. An aggressor with no data about the significant thing of the OCs can't figure the reasonable permit to free up the pilfered/overproduced chips. accordingly, the style planner is the best one who can trouble the permit to ignite off the chip. while the chip is turned on, the PUF response will XOR with the permit to create the ideal design for OCs, then, at that point, the produced arrangement is saved in the

flip-failures to deliver the chip. at the point when the chip is turned on, the PUF reaction will XOR with the permit to create the ideal key pieces for OCs, then the produced key pieces are saved inside the go failures to deliver the chip. The assailants can remove the jumbled entryway stage netlist with the guide of RE, but the extricated netlist doesn't integrate the key pieces.

We utilize the PUF response to deliver the component of the chip. The fashioner frequently registers the blunder amending code (ECC) to manage for any piece flips to the PUF yield (reaction) because of the reality the PUF yield is difficult to protect unquestionably stable in light of the clamor or various assets of actual vulnerability. note that, we don't report the upward of forcing PUFs and ECC strategies in this short. The upward for upholding PUF and ECC are with no difficulty accessible in cutting edge literary works summed up. the misstep rectified PUF response is utilized to open the component of the chip; without the ideal PUF reaction, the element could now not perform effectually. in this manner, the circuit is kept locked till the legitimate permit opens it. It must be refered to that the gave licenses likewise can be public and extraordinary PUF reactions can be utilized to compute exceptional licenses.

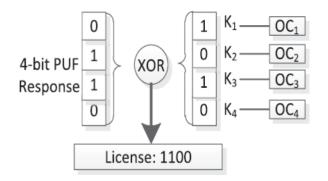

Figure 1 PUF-based obfuscation and the generation of the licenses.

to show the significant thing thought of our strategy, we convey a model for delivering the permit in recognize. contemplating 4 OCs in Fig, OC1-OC4 and K1-K4 are the vital pieces of the OCs. accept K1-K4 = 1010, the OC might be utilized to supplant any inverters or addition any wires. depend on that the PUF yield cost is 0110. To likely vigorous the chip, the 4-cycle PUF yield 0110 should be XOR'd with a four-digit permit this can create the final product of 1010 (in this present circumstance, the permit should be 1100). The chip can be accurately opened with the determined permit and the PUF reaction. The nonvolatile on-chip recollections could be utilized to store the PUF challenges, the permit, and the significant ECC bits on each appropriate actuated IC. Starting here on, each time the IC fires up, it could precisely peruse the PUF challenge and ECCs and use them to deliver the chip.

## RESULT AND DISCUSSIONS

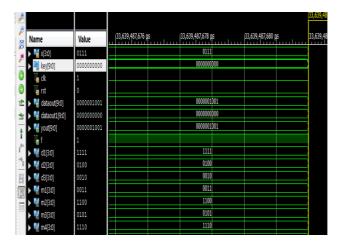

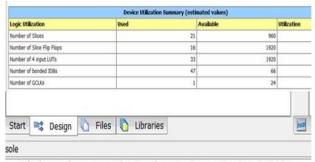

The proposed circuit are reenacted and integrated by means of the utilization of modelsim and xilinx12.1 individually. The reproduction results of design and the waveforms are demonstrated inside the fig.2 and fig three. Then table 1 is shown the consequence of current and proposed area utilization. The

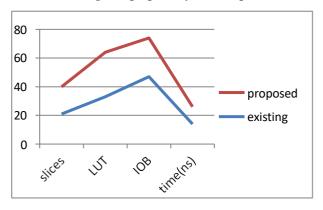

decide 4 and 4 are amalgamation record of current and proposed device. in the end the exhibition graph of this endeavor is demonstrated in recognize 6 separately.

Figure 2 Output without PUF

Minimum input arrival time before clock: 2.780ns Maximum output required time after clock: 12.725ns Maximum combinational path delay: 13.987ns

Figure 3 Output with PUF

|                            | Device Utilization Summary (esti                                                                    | mated values) |

|----------------------------|-----------------------------------------------------------------------------------------------------|---------------|

| Logic Utilization          | Used                                                                                                | Available     |

| Number of Slices           | 19                                                                                                  | 960           |

| Number of Slice Flip Flops | 16                                                                                                  | 1920          |

| Number of 4 input LUTs     | 31                                                                                                  | 1920          |

| Number of bonded IOBs      | 27                                                                                                  | 66            |

| Number of GCLKs            | 1                                                                                                   | 24            |

| nsole                      |                                                                                                     |               |

| Maximum output             | rrival time before clock: 2.780n<br>required time after clock: 11.39<br>tional path delay: 12.072ns |               |

Figure 4 existing synthesis report

Table 1 comparison table

| Table 1 comparison table |          |          |

|--------------------------|----------|----------|

| parameter                | existing | proposed |

|                          |          |          |

| slices                   | 21       | 19       |

|                          |          |          |

| LUT                      | 33       | 31       |

|                          |          |          |

| IOB                      | 47       | 27       |

|                          |          |          |

| time(ns)                 | 13.98    | 12.07    |

Figure 5 proposed synthesis report

Figure 6 performance chart

## **CONCLUSION**

In this paper, effectually planned a PUF based proof conveying AxCs. the use of this clever thought, makers of approximated IP centers provided formal guarantees for their circuits' slip-ups limits and clients empowered to confirm these bumbles limits without tolerating as obvious with the producer or transmission channels. Significantly, clients introduced the trust at a part of the computational exertion wanted for complete confirmation. We had affirmed a proof-conveying AxCs with seat mark channel plan, and tentatively settled the method.

#### REFERENCES

- [1] P. Yellu, M. R. Monjur, T. Kammerer, D. Xu and Q. Yu, "Security Threats and Countermeasures for Approximate Arithmetic Computing," 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), Beijing, China, 2020, pp. 259-264, doi: 10.1109/ASP-DAC47756.2020.9045385.

- [2] T. Song, Y. Xue and D. Wang, "An Algorithm of Large-Scale Approximate Multiple String Matching for Network Security," 2006 First International Conference on Communications and Networking in China, Beijing, 2006, pp. 1-5, doi: 10.1109/CHINACOM.2006.344838.

- [3] M. Gao, Q. Wang, M. T. Arafin, Y. Lyu and G. Qu, "Approximate computing for low power and security in the Internet of Things," in Computer, vol. 50, no. 6, pp. 27-34, 2017, doi: 10.1109/MC.2017.176.

- [4] P. Yellu, Z. Zhang, M. M. R. Monjur, R. Abeysinghe andQ. Yu, "Emerging Applications of 3D Integration and

- Approximate Computing in High-Performance Computing Systems: Unique Security Vulnerabilities," 2019 IEEE High Performance Extreme Computing Conference (HPEC), Waltham, MA, USA, 2019, pp. 1-7, doi: 10.1109/HPEC.2019.8916503.

- [5] H. Martin, L. Entrena, S. Dupuis and G. Di Natale, "A Novel Use of Approximate Circuits to Thwart Hardware Trojan Insertion and Provide Obfuscation," 2018 IEEE 24th International Symposium on On-Line Testing And Robust System Design (IOLTS), Platja d'Aro, 2018, pp. 41-42, doi: 10.1109/IOLTS.2018.8474077.

- [6] W. Liu, C. Gu, M. O'Neill, G. Qu, P. Montuschi and F. Lombardi, "Security in Approximate Computing and Approximate Computing for Security: Challenges and Opportunities," in Proceedings of the IEEE, doi: 10.1109/JPROC.2020.3030121.

- [7] M. Ye, X. Feng and S. Wei, "Runtime Hardware Security Verification Using Approximate Computing: A Case Study on Video Motion Detection," 2019 Asian Hardware Oriented Security and Trust Symposium (AsianHOST), Xi'an, China, 2019, pp. 1-6, doi: 10.1109/AsianHOST47458.2019.9006675.

- [8] Gupta and K. Suneja, "Hardware Design of Approximate Matrix Multiplier based on FPGA in Verilog," 2020 4th International Conference on Intelligent Computing and Control Systems (ICICCS), Madurai, India, 2020, pp. 496-498, doi: 10.1109/ICICCS48265.2020.9121004.

- [9] G. S. Rodrigues, J. Fonseca, F. Benevenuti, F. Kastensmidt and A. Bosio, "Exploiting Approximate Computing for Low-Cost Fault Tolerant Architectures," 2019 32nd Symposium on Integrated Circuits and Systems Design (SBCCI), Sao Paulo, Brazil, 2019, pp. 1-6

- [10] C. Li, D. Sengupta, F. S. Snigdha, W. Xu, J. Hu and S. S. Sapatnekar, "Special session: a quantifiable approach to approximate computing," 2017 International Conference on Compilers, Architectures and Synthesis For Embedded Systems (CASES), Seoul, 2017, pp. 1-2, doi: 10.1145/3125501.3125511.

- [11] S. Hashemi and S. Reda, "Generalized Matrix Factorization Techniques for Approximate Logic Synthesis," 2019 Design, Automation & Test in Europe Conference & Exhibition (DATE), Florence, Italy, 2019, pp. 1289-1292, doi: 10.23919/DATE.2019.8715274.

- [12] S. Lee, L. K. John, and A. Gerstlauer, "High-level synthesis of approximate hardware under joint precision and voltage scaling," in *Proc. Design, Autom. Test Eur. Conf. Exhibiting (DATE)*, Mar. 2017, pp. 187–192.

- [13] Jiang, H., Liu, L., & Han, J. (2017). An efficient hardware design for cerebellar models using approximate circuits. Proceedings of the Twelfth IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis Companion CODES '17. doi:10.1145/3125502.3125537

- [14] H. Saadat and S. Parameswaran, "Special session: hardware approximate computing: how, why, when and where?," 2017

International Conference on Compilers, Architectures and Synthesis For Embedded Systems (CASES), Seoul, 2017, pp. 1-2, doi: 10.1145/3125501.3125518.